International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19) 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

# **Analysis and Implementation of Multimode Interleaver for Wireless Communication**

N. Nagaraju<sup>1</sup>, R. Sahana<sup>2</sup>, N. S. Sharika<sup>3</sup>, M. Shilpa<sup>4</sup>, R. Tamil Selvi<sup>5</sup>

Assistant Professor, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

UG Student, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

**ABSTRACT:** In today's modern world Wireless communication is one of the most vibrant research areas in communication field. WiMAX and WLAN are emerging standards in wireless broadband communication system. The channel interleaver employed in the WiMAX transceiver plays a major role in minimizing the effect of burst error. Interleaving is a technique for making forward error correction more robust with respect to burst errors and to achieve more flexibility in the multimode interleaver address generator, an efficient matrix circuit are proposed to compute MOD function for Row and Column counter values in order to replace the memory. The proposed circuit is designed and synthesized using XILINX 12.3 ISE.

KEYWORDS: Wireless systems, Interleaver, error correction, address generator.

# I. INTRODUCTION

Broadband wireless access (BWA) systems have developed as the solution for the persistent demand of these multimedia services [10]. It provides improvement in multimedia data services. It supports synchronous voice, data and multimedia services for more users without the need for digital subscriber line (DSL) or cable modem. IEEE has developed standards (IEEE 802.11a/g) which are popularly known as wireless local area network (WLAN) and (IEEE 802.16e) known as mobile WiMAX [11]. The forward error correction (FEC) block uses more silicon due to addressing/permutation tables used in the conventional approaches for interleaver and de interleaver. To support the rapid development in wireless technology, the interleaver address generator hardware needs to convert to the interleaving standards.

The channel interleaver is a necessary block in the PHY of 802.11a/g and 802.16e based transmitter. In digital communication burst error occur, a number of random error correction codes have been succeed. ECC is not effective in combating bursts of errors. The paper is described as follows: Related works for WIMAX interleaver address generator is discussed in section 2. Section 3 explains the performance of the WiMAX transceiver system. In section 4 Interleaving in WIMAX system is explained. In Section 5 describes proposed architecture of mod circuits for interleaver address generator and its mathematical expression. Section 6 describe the simulation and synthesis result. Finally, this work is concluded in Section 7.

## **II. RELATED WORKS**

Very few works interconnected to hardware implementation of the interleaver/deinterleaver used in a WiMAX system is available in the literature. The authors have explained a finite-state machine (FSM)-based address generator of the similar interleaver for all allowable code rates and modulation schemes in [3].

The channel interleaver is a necessary block in the PHY of 802.11a/g and 802.16e based transmitter. A channel interleaver for multistandard SDR has to support multiple interleaving operations thus, interleaving plays a vital

Volume 8, Special Issue 1, March 2019

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

An ISO 3297: 2007 Certified Organization

# Organized by

## Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

role in improving the performance of FEC codes in terms of bit error rate. The basic function ofInterleaver block is to extend the encoded data into a random one. In the conventional approach, the received data is to be stored row-wise in the memory and read column-wise after applying certain permutations. To achieve more adaptability in the multimode interleaver, an address generator has to be developed using specialised blocks with reconfigurable ability and Upadhyaya et al have implemented the conventional interleaver on field programmable gate array (FPGA) with decrease in area in [5]. An address generating circuit, for 802.11 interleaver based on the conventional look up table (LUT) method is proposed in [8].

The author presented a high speed block interleaver/deinterleaver to give arbitrary column wise permutation by adopting a low-power first in first out bank structure and a simple finite state machine (FSM) in [6].

## **III. WIMAX TRANSRECEIVER**

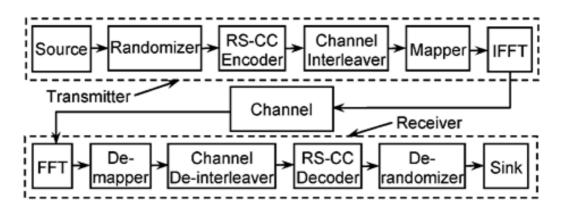

Fig 1 Block diagram of the WiMAX transceiver.

The system level overview of IEEE 802.16e based WiMAX system is shown in Fig.1. Pseudo Random Binary Sequence (PRBS) is utilized in which randomization is done by modulo 2addition of the data with the output of the PBRS itself [3]. The randomized data bits are encoded using Reed Solomon (RS) encoder followed by Convolutional Coder (CC). The former is acceptable for correction of burst type of error whereas the latter is for random error.

### **IV. INTERLEAVING IN WIMAX SYSTEM**

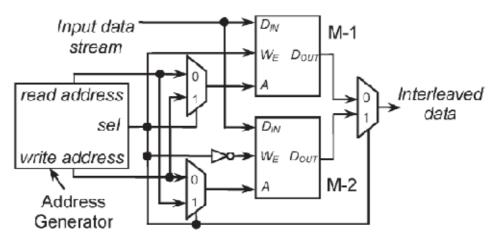

The channel interleaving is a process of rearranging code Symbols to decrease the effect of burst error. It processes one block of encoded bits at a time with block size equal to one OFDM symbol depending on the modulation design for a specific code rate. It consists of an address generator and two RAMs of the similar size. Both the memories are directed by the sel signal, generated from the address generator in such a way that when one memory block is being written, the other one is read, and vice versa. When sel = 'HIGH', the input data stream written in M1 relative to the write address as WE is active. z The read/write operation of memory blocks are moved out according to the interleaver depth. If it reaches the specified depth, then the status of sel signal is altered to swap the read/ write operation.

Volume 8, Special Issue 1, March 2019

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

An ISO 3297: 2007 Certified Organization

# Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Fig 2 Block diagram of interleaver

After RS-CC encoding all encoded data bits will be interleaved by a block interleaver. As soon memory is completely filled, the bits are read Column by column manner [3].

In the block interleaver of WiMAX system, data is written in the memory in a limited Manner based on certain arrangement and read in a sequential manner. After interleaving, data send through the mapper block in which modulation takes place. The resulting data symbols are used to construct one OFDM symbol by execute Inverse Fast Fourier Transform (IFFT). Cyclic Prefix (CP) is used to decrease ISI.

# V. PROPOSED MOD FUNCTION CIRCUIT

In this section, the architectural details of mod row and mod column for the multimode interleaver address generator is proposed. It incorporates row counter, column counter, selection unit, multiplier and an adder. The output of column counter is compared with d to produce a fixed count value between 0 to d - 1. Whereas, the row counter is a changeable one, which counts different levels between 0 to (Ncbps/d) – 1 based on particular block size selected by multiplexers (MUXs) M6 and M7.The addresses of 16-QAM and 64-QAM are not equally spaced.

Therefore, the address generator has to produce two cumulative patterns for 16-QAM and three for the 64-QAM modulation scheme. Thus, the design process adapted for QPSK can be extended to 16-QAM and 64-QAM with additional components such as incrementer, decrementer and a separate MOD circuit for row and column counter respectively. To ensure adaptability in generating address for different modulation schemes, MUX based logic is perceived to select incremented/ decremented values of row counter based on specific mod\_ type, MOD\_row and MOD\_column values.

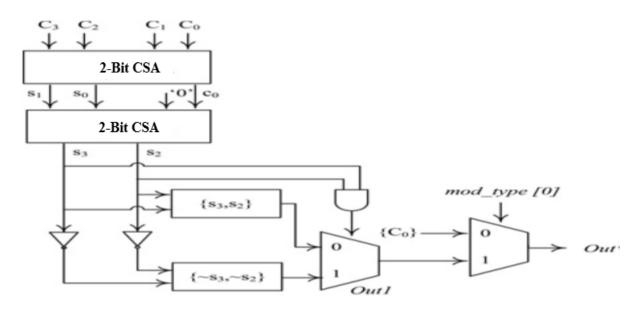

The requirement of MOD functions for column and row count values in the address generation of 16-QAM and 64-QAM are contented by the proposed MOD\_column and MOD\_row circuits as shown in Figs. 3 and 4 respectively. The proposed mod column and mod\_ row circuit using carry save adder reduces the propagation delay compared to existing mod circuit

# A. OPERATION OF MOD\_COLUMN

As, the number of column (d) is chosen as 16, the column counter values moves between 0 to (d - 1), that is, maximum value of 15. Hence, a 4-bit MOD\_column circuit is proposed to determine the MOD value of column counter as shown in Fig. 3 With the 4-bit input as C3, C2, C1 and C0 from MSB to LSB. The final MOD2 or MOD3 value for the column counter is obtained by performing the consecutive steps as shown in Table 1.

Volume 8, Special Issue 1, March 2019

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

## Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

### 1). LOGICAL EXPRESSION FOR MOD\_COLUMN

An ISO 3297: 2007 Certified Organization

The four bit inputs (C3, C2, C1, C0) grouped into two 2-bit numbers. To obtain the Boolean expression of the sum (s1, s0) and carry (c0) of the first 2-bit adder in Fig. 3, the variables (B1, B0, A1,A0) in (11), (12) and (13) are substituted with (C3, C2, C1, C0).

$$\begin{split} s1 &= C3 \cdot C2 \cdot C1 + C3 \cdot C1 \cdot C0 + C3 \cdot C2 \cdot C1 \cdot C0 \\ &+ C3 \cdot C2 \cdot C1 + C3 \cdot C1 \cdot C0 + C3 \cdot C2 \cdot C1 \cdot C0 \\ s0 &= C2 \cdot C0 + C2 \cdot C0 \ (15) \\ c0 &= C2 \cdot C1 \cdot C0 + C3 \cdot C1 + C3 \cdot C2 \cdot C0 \end{split}$$

Similarly, the Boolean expression of sum (s3, s2) of the second 2-bit adder in Fig. 3, can be obtained by replacing the values of

(s1, s0, 0, c0) in the place of (B1, B0, A1, A0) in (11), (12) and (13).

$s3=C3\cdot C2\cdot C1\cdot C0+C3\cdot C2\cdot C1+\cdot C2\cdot C1\cdot C0+C3\cdot C2\cdot C1\\+C3\cdot C1\cdot C0+C1\cdot C3\cdot C0$

$s2=C3 \cdot C2 \cdot C1 \cdot C0 + C3 \cdot C2 \cdot C0 + C3 \cdot C2 \cdot C0 + C2 \cdot C1 \cdot C0$ + C2 \cdot C1 \cdot C0 + C3 \cdot C1 \cdot C0

From the Table 1, it is noted that the sum value (s3, s2) correspond with the MOD3 (modulo 3) of the 4-bit inputs, except for the case of sum value is 3 ('11'). Where, the necessary MOD3 value is 0 ('00'), that is, complement. The key point is, if the sum value goes to '3' we have to bring into '0'. Hence, we introduced a MUX for choosing either the direct value of sum (s3, s2) or its complement value ( $\_$  s3,  $\_$  s2) with the control signal (sel) generated by performing AND operation of the mux.

Fig 3 Proposed architecture of MOD\_column circuit with 4-bit input

Finally, the output of the MOD\_column is obtained by selecting either MOD2 (C0) or MOD3 (Out1) with selection signal as mod type[0].

Volume 8, Special Issue 1, March 2019

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

An ISO 3297: 2007 Certified Organization

# Organized by

## Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

| STEP | For the count value of 12.                                          | Output                                                 | Operation                                                                                      |

|------|---------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------|

|      | 12.                                                                 |                                                        |                                                                                                |

| 1    | 12 = '1100' as 11 00                                                | $C_1 C_0 = 00 \ C_3 C_2$<br>= 11                       | Group in to two bits<br>each                                                                   |

|      | $C_1 C_0 = 00$                                                      | <i>s</i> <sub>1</sub> <i>s</i> <sub>0</sub> = 11 (sum) | 2-bit ripple carry                                                                             |

| 2    | $+C_3C_2=11$                                                        | $c_0 = 0$ (carry)                                      | addition                                                                                       |

|      | 0) 11                                                               |                                                        |                                                                                                |

|      | $s_1 s_0 = 11$                                                      | MSB is fixed to                                        | 2-bit ripple carry                                                                             |

| 3    | $+0 c_0 = 00$                                                       | '0' s <sub>3</sub> s <sub>2</sub> = 11                 | addition                                                                                       |

|      | 0) 11                                                               | (sum)                                                  |                                                                                                |

| 4    | If $s_3 s_2 = 11$ ,                                                 | Out1 = 00, that                                        | Complement                                                                                     |

|      | complement each bit;                                                | is, MOD3 value                                         |                                                                                                |

|      | Else, pass the same.                                                |                                                        |                                                                                                |

| 5    | C <sub>0</sub> represents MOD2                                      | $C_0 = 0$ , that is,                                   |                                                                                                |

|      | value                                                               | MOD2 value                                             |                                                                                                |

| 6    | Final MUX with the<br>selection line as<br>mod_type[0] <sup>a</sup> | mod_type[0] = 0<br>for 64-QAM                          | $\begin{array}{l} \text{MOD\_column} \\ \text{Output, that is, } Out \\ = C_0 = 0 \end{array}$ |

| Table 1 Working of proposed MOD_column circuit |

|------------------------------------------------|

|------------------------------------------------|

| Table 2 Truth table for th | e MOD_column circuit |

|----------------------------|----------------------|

|----------------------------|----------------------|

| <i>C</i> <sub>3</sub> | <i>C</i> <sub>2</sub> | <i>C</i> <sub>1</sub> | Co | <i>s</i> <sub>1</sub> | <i>S</i> 0 | <b>'0'</b> | C <sub>0</sub> | <i>S</i> <sub>3</sub> | <i>s</i> <sub>2</sub> | sel | MC | D3 | MOD2 |

|-----------------------|-----------------------|-----------------------|----|-----------------------|------------|------------|----------------|-----------------------|-----------------------|-----|----|----|------|

| 0                     | 0                     | 0                     | 0  | 0                     | 0          | 0          | 0              | 0                     | 0                     | 0   | 0  | 0  | 0    |

| 0                     | 0                     | 0                     | 1  | 0                     | 1          | 0          | 0              | 0                     | 1                     | 0   | 0  | 1  | 1    |

| 0                     | 0                     | 1                     | 0  | 1                     | 0          | 0          | 0              | 1                     | 0                     | 0   | 1  | 0  | 0    |

| 0                     | 0                     | 1                     | 1  | 1                     | 1          | 0          | 0              | 1                     | 1                     | 1   | 0  | 0  | 1    |

| 0                     | 1                     | 0                     | 0  | 0                     | 1          | 0          | 0              | 0                     | 1                     | 0   | 0  | 1  | 0    |

| 0                     | 1                     | 0                     | 1  | 1                     | 0          | 0          | 0              | 1                     | 0                     | 0   | 1  | 0  | 1    |

| 0                     | 1                     | 1                     | 0  | 1                     | 1          | 0          | 0              | 1                     | 1                     | 1   | 0  | 0  | 0    |

| 0                     | 1                     | 1                     | 1  | 0                     | 0          | 0          | 1              | 0                     | 1                     | 0   | 0  | 1  | 1    |

| 1                     | 0                     | 0                     | 0  | 1                     | 0          | 0          | 0              | 1                     | 0                     | 0   | 1  | 0  | 0    |

| 1                     | 0                     | 0                     | 1  | 1                     | 1          | 0          | 0              | 1                     | 1                     | 1   | 0  | 0  | 1    |

| 1                     | 0                     | 1                     | 0  | 0                     | 0          | 0          | 1              | 0                     | 1                     | 0   | 0  | 1  | 0    |

| 1                     | 0                     | 1                     | 1  | 0                     | 1          | 0          | 1              | 1                     | 0                     | 0   | 1  | 0  | 1    |

| 1                     | 1                     | 0                     | 0  | 1                     | 1          | 0          | 0              | 1                     | 1                     | 1   | 0  | 0  | 0    |

| 1                     | 1                     | 0                     | 1  | 0                     | 0          | 0          | 1              | 0                     | 1                     | 0   | 0  | 1  | 1    |

| 1                     | 1                     | 1                     | 0  | 0                     | 1          | 0          | 1              | 1                     | 0                     | 0   | 1  | 0  | 0    |

| 1                     | 1                     | 1                     | 1  | 1                     | 0          | 0          | 1              | 1                     | 1                     | 1   | 0  | 0  | 1    |

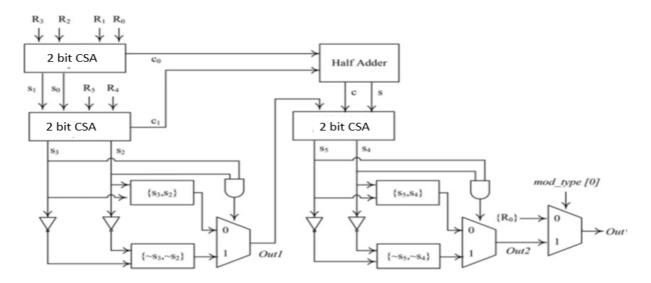

## **B. OPERATION OF MOD\_ROW**

The maximum block size (Ncbps) for IEEE 802.11a/g and IEEE 802.16 interleaver is 576. Therefore, the row counter counts maximum value of (Ncbps/d) - 1 = 35. In binary form can be represented with 6-bit as '100011'. Hence, a MOD row circuit is proposed to compute MOD function for 6-bit input named as R5, R4, R3, R2, R1, R0 from MSB to LSB as shown in Fig. 4.

An ISO 3297: 2007 Certified Organization Volume 8, Special Issue 1, March 2019

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

# Organized by

## Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Fig 4 Proposed architecture of MOD row circuit with 6-bit input

The final MOD2 or MOD3 for the row counter is obtained by performing the successive steps as shown in Table 7. The Boolean expression for the MOD row circuit can be derived in the same manner as MOD column. The MUX selects either the direct value of sum (s5, s4) or its complement value ( $\_$  s5,  $\_$  s4) with the selection signal (sel) obtained by performing AND operation of the sum bit s5 and s4 as given in Fig. 4.

Finally, the output of the MOD row (Out) is generated by selecting either MOD2 values (R0) or the MOD3 value (Out2) with the selection signal as mod type [0].

The proposed MOD circuit for row and column, eliminates the need for two ROMs of dimension  $16 \times 3$ -bit and  $64 \times 3$ -bit in to store the MOD values for 16-QAM and 64-QAM respectively, which yields a large amount of reduction in resources and improvement in performance.

| STEP | For the count value of 35.                                                             | Output                                                                       | Operation                                         |

|------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------|

| 1    | 35 = '100011' as 10 00 11                                                              | $\begin{array}{l} R_1 R_0 = 11 \ R_3 R_2 \\ = 00 \ R_5 R_4 = 10 \end{array}$ | Group in to two<br>bits each                      |

| 2    | $ \begin{array}{r} R_1R_0 = 11 \\ + R_3R_2 = 00 \\ 0) 11 \end{array} $                 | $s_1 s_0 = 11 \text{ (sum)}$<br>$c_0 = 0 \text{ (carry)}$                    | 2-bit ripple carry<br>addition                    |

| 3    | $s_1 s_0 = 11 + R_5 R_4 = 10 = 10 = 10 = 10$                                           | $s_3 s_2 = 01 \text{ (sum)}$<br>$c_1 = 1 \text{ (carry)}$                    | 2-bit ripple carry<br>addition                    |

| 4    | If $s_3s_2 = 11$ , complement<br>each bit; Else, pass the<br>same.                     | <i>Out1</i> = 01                                                             | No Complement                                     |

| 5    | $c_0 = 0 + c_1 = 1$<br>0) 1                                                            | s = 1 (sum) c = 0<br>(carry)                                                 | Half adder                                        |

| 6    | c s = 01 + Out1 = 01 = 01 = 0) 10                                                      | s <sub>5</sub> s <sub>4</sub> = 10 (sum)                                     | 2-bit ripple carry<br>addition                    |

| 7    | If s <sub>5</sub> s <sub>4</sub> = 11, complement<br>each bit; Else, pass the<br>same. | <i>Out2</i> =10, that is, MOD3 value                                         | No Complement                                     |

| 8    | R <sub>0</sub> represents MOD2                                                         | $R_0 = 0$ , that is,                                                         |                                                   |

| 9    | value<br>Final MUX with the<br>selection line as<br><i>mod_type</i> [0] <sup>a</sup>   | MOD2 value<br>mod_type[0] = 1<br>for QPSK                                    | MOD_column<br>Output, that is,<br>Out = '10' = 2. |

Volume 8, Special Issue 1, March 2019

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

An ISO 3297: 2007 Certified Organization

## Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

## VI.SIMULATION RESULT

In this section, the performance analysis of the proposed MOD function circuit using carry save adder are discussed. In [2], Butler & et al have developed two methodologies for computing x mod z with z fixed as 3, where x is the n-bit input and z is the MOD value. First perspective is based on combinational circuits and the second design uses cascade of LUTs. The proposed MOD circuit is much faster, consumes fewer resources and it reduces the propagation delay than the first approach in [2].

From the results, it is concluded that for higher input bit width, the proposed circuit extends further reduction in resource utilization and improvement in operating speed. Compared with the second design using LUTs, our proposed design consumes less logic resources.

| ADDERS                 | RIPPLE CAR<br>ADDER | RRY        | CARRY SEI<br>ADDER | LECT       | CARRY LO<br>AHEAD AD |            | CARRY SAVE<br>ADDER(PROPOSED) |            |  |

|------------------------|---------------------|------------|--------------------|------------|----------------------|------------|-------------------------------|------------|--|

|                        | MOD<br>COLUMN       | MOD<br>ROW | MOD<br>COLUMN      | MOD<br>ROW | MOD<br>COLUMN        | MOD<br>ROW | MOD<br>COLUMN                 | MOD<br>ROW |  |

| No. of slices          | 1                   | 4          | 3                  | 8          | 5                    | 7          | 1                             | 3          |  |

| No. of LUTS            | 2                   | 7          | 5                  | 14         | 9                    | 13         | 2                             | 6          |  |

| No. of bonded<br>IOB's | 8                   | 10         | 8                  | 11         | 9                    | 11         | 9                             | 12         |  |

| No. of<br>GCLK's       | 1                   | 1          | 1                  | 1          | 1                    | 1          | 1                             | 1          |  |

Table 4 Comparison of mod function circuit using different adder

The comparison table for mod function circuit are given in table 4.Since, the LUT approach adapts LUT in each stage rather than combinational logic, the design able to operate at high speed with increase in latency. Mod circuit using carry save adder increase the speed and efficiency by reducing the number of slices. The design is simulated on Xilinx 12.3 ISE to have a better comparison of the proposed work with the existing approaches in [1].

|               |       |      |      | 3.405400 us | 5   |       |       |      |      |

|---------------|-------|------|------|-------------|-----|-------|-------|------|------|

| Name          | Value |      | 3 us | 1           | 4us | 15 us | 16 us | 7us  | 8 us |

| 🕨 📑 c[3:0]    | 1001  | 1000 |      | 10          | 01  | 11    | po    | 1111 |      |

| 🔓 mod_type    | 0     |      |      |             |     |       |       |      |      |

| 🕨 📷 out1[1:0] | 11    | 10   |      | 11          |     | 00    |       | 01   | 00   |

| 1 a1          | 1     |      |      |             |     |       |       |      |      |

| 🕨 式 s[3:0]    | 0011  | 0010 |      |             | 00  | 11    |       | 0110 |      |

| 🕨 式 su[1:0]   | 11    | 10   |      |             | 1   | 1     |       | 11   |      |

| 🕨 📲 i[1:0]    | 00    | 01   |      |             | 0   | p     |       | 00   |      |

| 🕨 📲 j[1:0]    | 00    | 10   |      |             | 0   | p     |       | 00   |      |

|               |       |      |      |             |     |       |       |      |      |

Fig 5 Simulation result for mod column circuit

Volume 8, Special Issue 1, March 2019

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

An ISO 3297: 2007 Certified Organization

## Organized by

# Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

|               |             |              |             |          | 3,841.753 ns |          |              |          |  |  |  |

|---------------|-------------|--------------|-------------|----------|--------------|----------|--------------|----------|--|--|--|

| Name          | Value       | <br>2,500 ns | 3,000 ns    | 3,500 ns |              | 4,000 ns | 4,500 ns     | 5,000 ns |  |  |  |

| 🕨 📑 r[5:0]    | 100011      |              | 100011      |          |              | *        | 000000       |          |  |  |  |

| 🔓 mod_type    | 0           |              |             |          |              |          |              |          |  |  |  |

| 🕨 📑 out2[1:0] | 11          | 10           | *           |          |              | 11       |              | 00       |  |  |  |

| ▶ 📲 x[12:1]   | 00010100001 | 0            | 00101000010 |          |              | X        | 000000000000 |          |  |  |  |

| 🕨 式 s[3:0]    | 0011        |              | 0011        |          |              | X        | 0000         |          |  |  |  |

| 🕨 式 su[1:0]   | 01          |              | 01          |          |              | X        | 00           |          |  |  |  |

| 🕨 📲 i[1:0]    | 10          |              | 10          |          |              | X        | 11           |          |  |  |  |

| 🕨 📲 j[1:0]    | 01          |              | 01          |          |              | X        | 00           |          |  |  |  |

| 🕨 式 va[1:0]   | 10          |              | 10          |          |              | X        | 00           |          |  |  |  |

| 🕨 📲 ki[1:0]   | 01          |              | 01          |          |              | XX       | 11           |          |  |  |  |

| 🕨 式 mxt[1:0]  | 10          |              | 10          |          |              | XX       | 00           |          |  |  |  |

| 🕨 式 sum[5:4]  | 10          |              | 10          |          |              | X        | 00           |          |  |  |  |

|               |             |              |             |          |              |          |              |          |  |  |  |

Fig 6 Simulation result for mod row circuit

## **VII. CONCLUSION**

In this paper, an efficient mod function circuit for reconfigurable address generator architecture of multimode interleaver for IEEE 802.11a/g and 802.16e wireless standards supporting all possible code rates and modulation schemes has been presented. An efficient MOD row and a MOD column circuits were proposed to compute MOD function for row and column counter values. The synthesis results of the proposed MOD circuit using carry save adder shows significant reduction in resource utilization, improvement in operating speed compared with existing modulo algorithms and reduces the propagation delay.

#### REFERENCES

- [1] Gorodecky. D.A: "Reed-Müller realization of X (mod P)", CoRR, 2015, abs/1504.04773,- arxiv.org

- [2] Butler. J.T, Sasao, T: "Fast hardware computation of x mod z". Proc. 18<sup>th</sup> Reconfigurable Architectures Workshop (RAW 2011), Anchorage, Alaska, USA, May 2011, pp. 294–267

- [3] B. K. Upadhyaya& I. S. Misra, "Novel design of address generator for WiMAX multimode interleaver using FPGA based finite state machine", in Proc. 13th Int. Conf. Compute. Inf. Technol., Dhaka, Bangladesh, 2010, pp. 153–158.

[4] A. A. Khater, & M. M. Khairy, "Efficient FPGA implementation for the IEEE 802.16e interleaver, in Proc. Int. Conf. Micro-electron., Marrakech, Morocco", 2009, pp. 181–184.

[5] Upadhyaya. B.K, Sanyal. S.K: "VHDL modeling of convolutional interleaver- deinterleaver for efficient FPGA implementation", Int. J. Recent Trends Eng., 2009, 2, (6), pp. 66–68

[6] Yu. C, Yen. M.H, Hsiung, P.A: "Design of a high-speed block interleaving/ deinterleaving architecture for wireless communication applications". Proc. Int. Conf. Consumer Electronics, Las Vegas, USA, January 2009, pp. 1–2

[7] Asghar. R, Liu, D: "2D realization of WiMAX channel interleaver for efficient hardware implementation". Proc. World Academy of Science and Engineering Technology, Hong Kong, April 2009, pp. 25–29.

[8] Sghaier. A, Ariebi. S, Dony. B: "A pipelined implementation of OFDM transmission on reconfigurable platforms". Canadian Conf. on Electrical and Computer Engineering, December 2007, pp. 801–804

[9] Y. N. Chang & Y. C. Ding, "A low-cost dual mode de interleaver de-sign, in Proc Int. Conf. Consum. Electron". 2007, pp. 1–2.

[10]Konhauser. W "Broadband wireless access solutions" -Progressive challenges and potential value of next generation, Wireless Pers. Commun. Vol. 37, no. 3/4, pp. 243–259, May 2006.

[11] IEEE 802.16e: "Local and metropolitan networks-part 16: air interface for fixed broadband wireless access systems", 2005